01. Overview

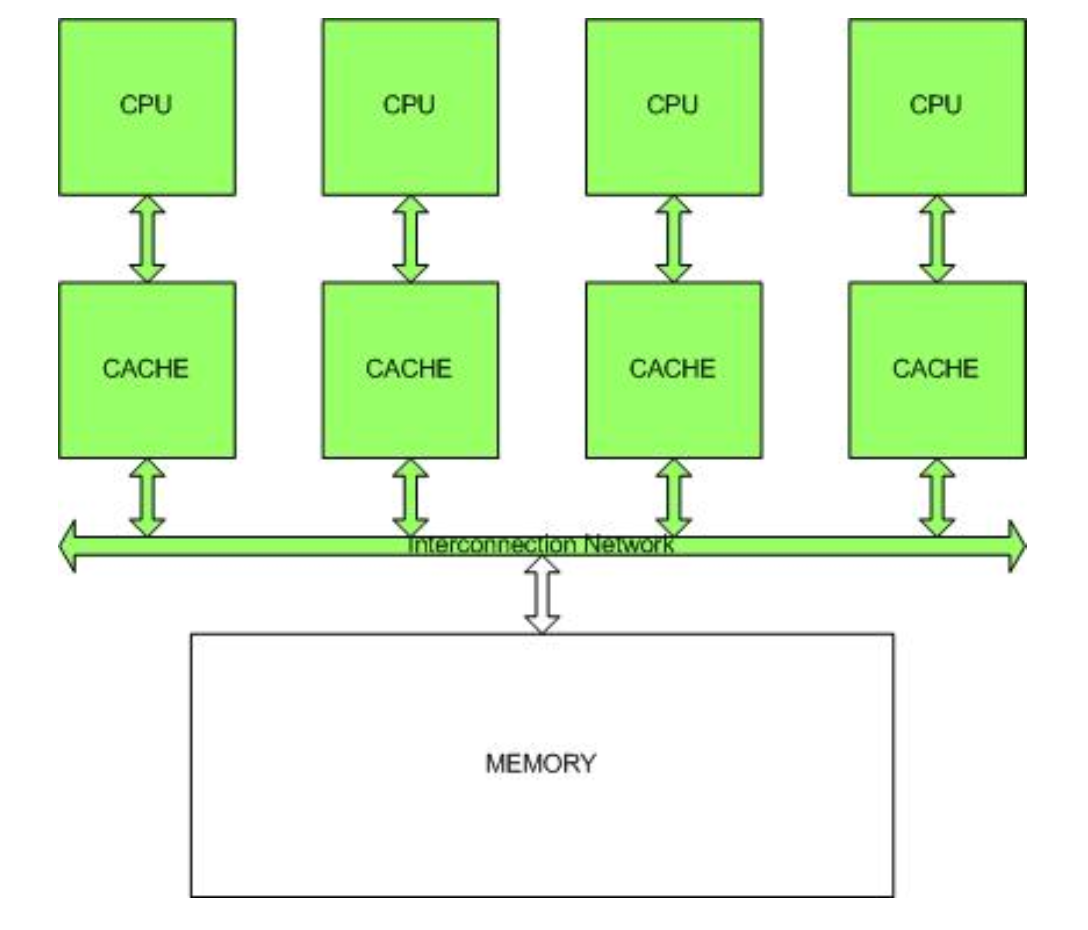

A modular, cycle-accurate simulator for multi-core processor systems built using SystemC. This project models complex memory hierarchies to simulate data consistency across 1 to 8 processors sharing a single bus and main memory.

The simulator is driven by real-world memory trace files (Matrix Multiplication, FFT) to evaluate performance metrics like Hit/Miss rates and Bus Contention.

02. Architecture

The system implements a Shared Memory Architecture. It supports multiple processors working in parallel, each associated with a local L1 Data Cache.

- L1 Cache: 32kB, 8-way set-associative with a 32-Byte line size.

- Policy: Least-Recently-Used (LRU) write-back with allocate-on-write.

- Bus: A custom split-transaction bus handling memory latency (100 cycles).

03. Protocols Implemented

A. VALID - INVALID (VI)

The baseline implementation. A simple snooping protocol where cache lines toggle between Valid and Invalid states. While easy to implement, experiments showed it generates significant bus traffic due to frequent invalidations.

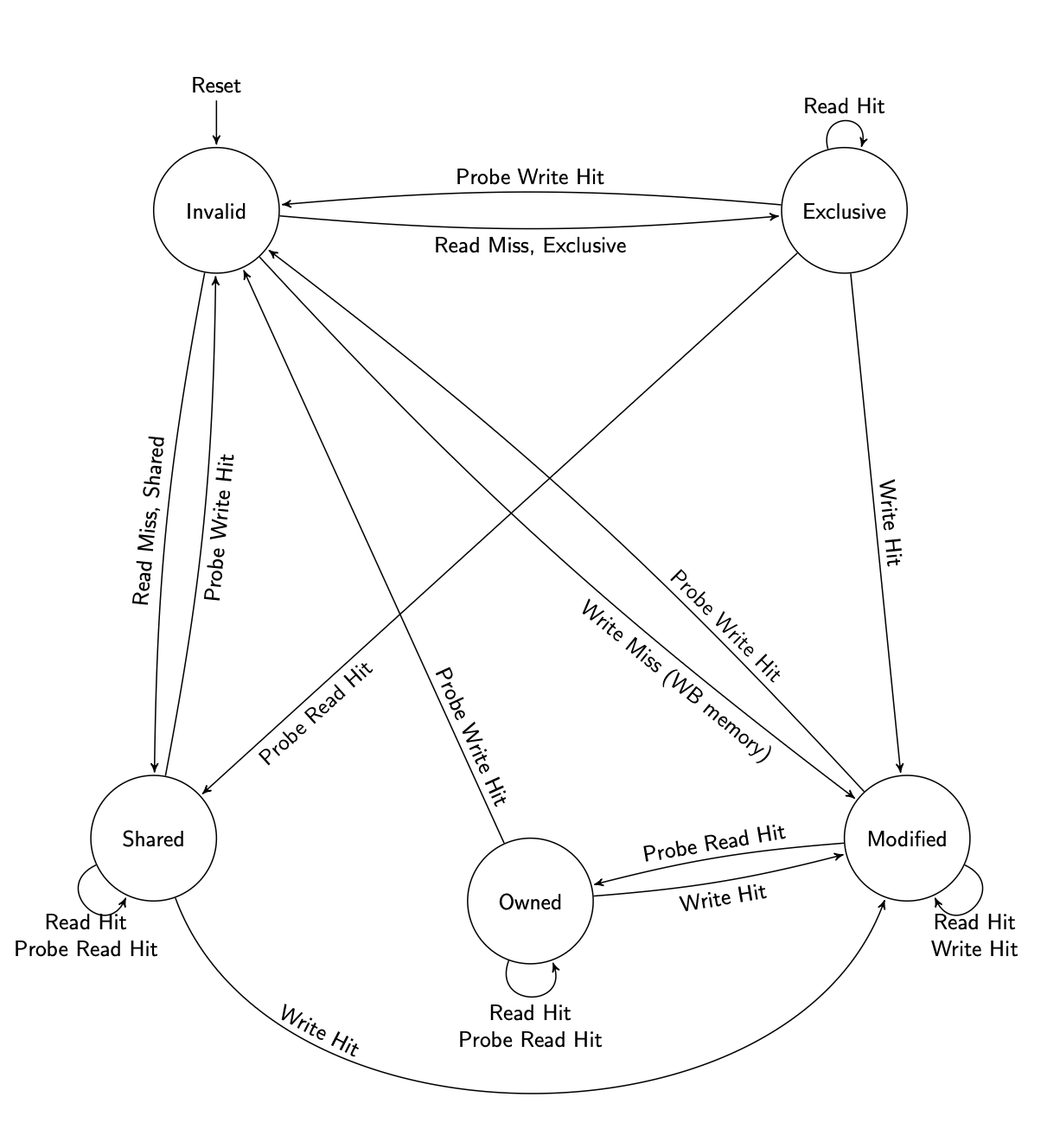

B. MOESI Protocol

An advanced protocol found in AMD64 architectures. It introduces the Owned and Exclusive states to optimize sharing.

- Owned (O): Allows data to be shared without writing back to main memory immediately.

- Optimization: Implemented cache-to-cache transfers, bypassing slow main memory access.